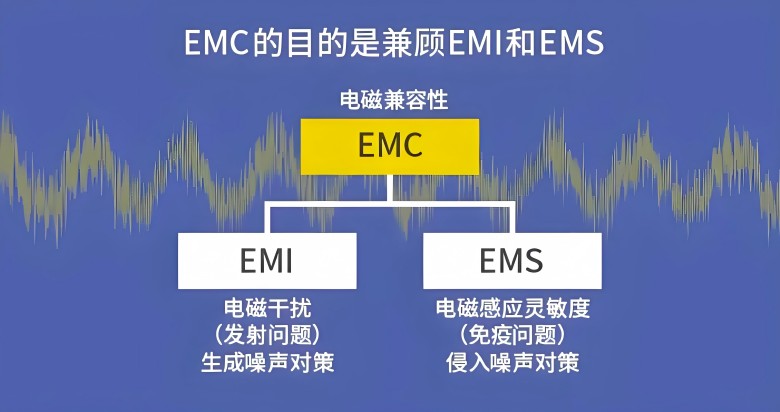

ESD静电放电抗扰度整改方案

ESD 静电放电抗扰度不达标核心整改思路是"阻、隔、泄、吸、地" 结合,先通过测试定位放电失效点

(接触 / 空气放电、放电位置、失效现象),再从硬件电路、结构屏蔽、接地布线、软件容错四方面针对性整改,最终通过复测验证效果。

方法论:先定位→再整改→后验证,避免盲目操作

第一步:精准定位失效问题(整改前提)

⚠️ 无定位的整改都是无效操作

1.1 必确认的核心测试信息

| 维度 | 具体内容 | 整改方向 |

|---|---|---|

| 放电类型 | 接触放电 / 空气放电 | 接触放电侧重“泄放+阻抗匹配”;空气放电侧重“屏蔽+间隙隔离” |

| 放电等级 | 如2kV接触、4kV空气 | 明确目标整改等级 |

| 失效位置 | 外壳按键/接口/指示灯/金属边框/散热孔 | ESD最易侵入的薄弱点 |

| 失效现象 | 死机/重启/数据丢失/功能异常/指示灯闪烁/电路烧毁 | 判断“信号串扰”还是“电源浪涌” |

| 失效链路 | 电荷传播路径(如按键→GPIO→主控) | 定位核心侵入通道 |

1.2 快速定位方法

- 接触放电:金属电极直接接触,失效说明有导电通路直通内部 → 需“泄放+隔离”

- 空气放电:电极保持间隙(如5mm)放电,失效说明电场耦合强 → 需“屏蔽+增大爬电距离”

- 分段排查:断开外部接口/屏蔽外壳,单独测试内部电路,判断“外部侵入”还是“内部抗扰不足”

第二步:分场景硬件整改(核心手段)

✅ 90%的ESD问题可通过硬件解决

2.1 外部接口整改(USB/网口/串口/HDMI/电源口)

策略:分层防护 + 泄放接地 + 阻抗匹配

通用防护方案

| 接口类型 | 防护器件选型 | 布线要求 |

|---|---|---|

| USB/串口(低速) | D+/D-串0Ω电阻/磁珠(100Ω~1kΩ),并接ESD二极管(如阿赛姆的ESD5D150TA);VCC并接MOV+陶瓷放电管 | 器件紧靠接口(≤5mm),TVS负极接信号地,磁珠靠近芯片端 |

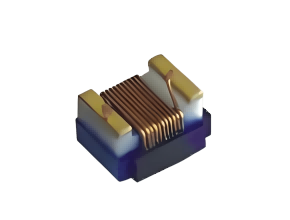

| 网口(RJ45) | 集成ESD防护的RJ45连接器(内置TVS+共模电感),差分线串共模电感(100~200nH) | 差分线等长,远离电源,共模电感紧靠网口,外壳360°接地 |

| 电源口(DC/AC) | DC口:TVS+MOV+PTC;AC口:陶瓷放电管+MOV+共模电感 | 电源地与机壳地单点连接,器件紧靠入口,布线横平竖直 |

| HDMI/DP(高速) | 高速ESD二极管(如ESD0524UA,Cj<5pF),差分线串高频磁珠 | 高速线减少过孔,器件紧靠接口,避免路径过长 |

核心原则

- 近接口、远芯片:防护器件必须紧靠接口,避免电荷在布线中传播耦合

- 高速信号禁忌:严禁用普通TVS,必须选"低结电容(<5pF)"高速器件

2.2 按键/指示灯/金属按钮整改

策略:GPIO隔离 + 电荷泄放 + 增大爬电距离

| 部件 | 具体方案 |

|---|---|

| 按键 | 并接ESD二极管(0402封装,如ESD5D150TA)或100pF~1nF高压陶瓷电容;引脚串1kΩ~10kΩ限流电阻;金属外壳可靠接机壳地 |

| 指示灯 | LED引脚串100Ω~1kΩ限流电阻,并接ESD二极管;金属外壳接地;与主控板爬电距离≥0.8mm |

| 核心原则 | GPIO不直接接外部金属件,通过“电阻+电容+ESD管”三级防护,阻断电荷进入主控 |

2.3 金属外壳/边框/散热孔整改(空气放电重灾区)

策略:全屏蔽 + 可靠接地 + 隔离间隙

| 部件 | 整改措施 |

|---|---|

| 金属外壳 | 多点可靠接地(≥2点),用"宽铜皮(≥2mm)"或金属弹片低阻抗连接 |

| 散热孔 | 改为圆形小孔阵列(孔径≤1mm,间距≥2mm);内侧贴金属屏蔽网并接机壳地 |

| 金属件隔离 | 内部金属件与电路板间加绝缘垫片(聚四氟乙烯/环氧树脂,≥0.5mm),增大爬电距离 |

2.4 内部电路整改(电源/主控/信号链路)

| 电路类型 | 整改措施 |

|---|---|

| 电源电路 | 输入端共模电感+差模电容(π型滤波);芯片供电端并接0.1μF+10μF高频去耦电容(紧靠VCC引脚);大功率电源加屏蔽罩 |

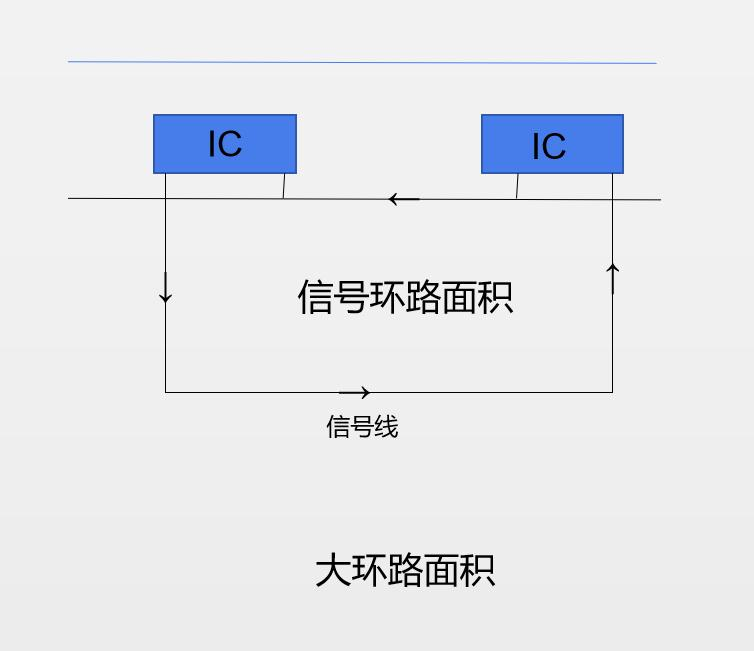

| 信号链路 | 差分信号串共模电感,单端信号串磁珠/限流电阻;敏感信号(时钟)用屏蔽线(屏蔽层单端接地);信号线远离金属外壳 |

| 芯片防护 | VCC/RESET/NMI等关键引脚并接小型ESD二极管;RESET引脚加RC延时(1kΩ+0.1μF);芯片周围做保护环接地 |

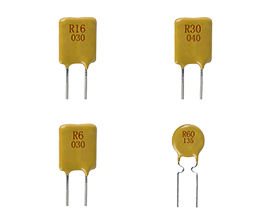

2.5 防护器件选型原则(避坑关键)

| 选型维度 | 具体要求 |

|---|---|

| 耐压值 | 2kV接触放电选5V耐压TVS,4kV选12V耐压 |

| 结电容 | 高速信号必须Cj<5pF,普通信号可放宽 |

| 封装 | 优先0402/0603贴片,紧靠接口/引脚焊接,减少寄生电感 |

| 应用范围 | 仅对外部引脚/敏感引脚防护,避免过度设计 |

| 品牌选择 | 推荐阿赛姆(ASIM)、村田、硕凯、安森美等正品,避免劣质器件 |