CMOS电路如何设计ESD保护结构?-ASIM阿赛姆

CMOS电路ESD保护结构设计指南

——芯片级静电防护核心技术解析

在纳米级CMOS工艺中,静电放电(ESD)已成为芯片失效的首要因素。据统计,ESD导致的IC损坏占现场故障的60%以上。本文将深入解析CMOS电路ESD保护结构的设计原理、关键技术与工程实践,助力提升芯片可靠性。

一、ESD失效机制与防护等级标准

主要失效模式

- 栅氧击穿(场强 >10 MV/cm):ESD脉冲导致栅氧永久性损坏(90nm以下工艺高发)。

- 寄生双极导通:ESD电流触发寄生NPN/PNP管,引发闩锁效应(Latch-up)。

- 金属熔毁:大电流(>1A)使互连线发生电迁移失效。

行业测试标准

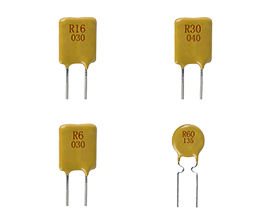

标准 测试模型 工业级要求 HBM 人体放电模型 ≥2kV(JEDEC JS-001) CDM 充电器件模型 ≥500V(JESD22-C101) MM 机器模型 ≥200V(EIA/JESD22-A115)

二、核心ESD保护结构设计

初级防护:输入/输出(I/O)Pad保护

- 原理:ESD触发寄生NPN管(源极-衬底-漏极),形成低阻通路。

- 关键设计参数:

- 触发电压:8-10V(65nm工艺)。

- 漏极扩散区长度 ≥ 0.5μm(避免局部热点)

- 多指状布局(降低导通电阻)

- 原理:利用PN结正向导通/反向雪崩泄放ESD电流。

- 连接方式:

- 优势:低电容(<1pF),适用于高速接口(USB/HDMI)。

- 局限:钳位电压较高(典型值0.7V + N×击穿电压)。

- Pad → 二极管阳极 → VSS(地)

- Pad → 二极管阴极 → VDD(电源)

二极管串结构

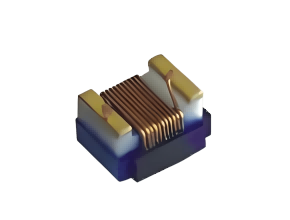

栅接地NMOS(GGNMOS)

次级防护:电源钳位(Power Clamp)

- 原理:PNPN结构触发后进入负阻区,实现超低钳位电压(1~2V)。

- 优势:单位面积电流能力提升5倍(vs. GGNMOS)。

- 挑战:需精确控制触发电压(Vt1)与维持电压(Vh)。

- 工作原理:

- 设计要点:

- ESD脉冲 → RC网络延迟 → 反相器 → 导通大尺寸MOSFET泄放电流

- MOSFET宽长比W/L ≥ 1000(65nm工艺)

- RC时间常数0.1~1μs(远大于ESD脉宽)

RC触发MOSFET型

SCR(硅控整流器)型

三、先进工艺设计挑战与解决方案

FinFET工艺难点

- 3D堆叠二极管结构

- 分布式SCR单元布局

- 鳍式结构散热能力下降 → ESD电流密度需<10 mA/μm

- 解决方案:

高压接口防护(如USB PD)

- 级联GGNMOS(Stacked GGNMOS)

- 自触发隔离技术

- 挑战:工作电压5V~20V,传统结构无法满足高压ESD需求。

- 方案:

四、ESD设计验证流程

TCAD仿真:

- 模拟ESD电流路径与温度分布(工具:Sentaurus/Silvaco)

- 优化目标:峰值温度 < 1414℃(硅熔点)

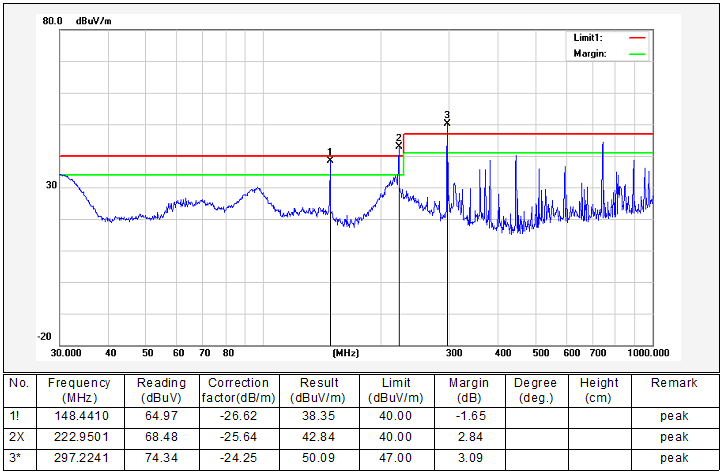

TLP测试(传输线脉冲):

- 触发电压Vt1

- 维持电流Ih

- 失效电流It2

- 关键参数提取:

- 标准:ESDA SP5.5.1

芯片级测试:

- HBM/CDM测试覆盖率100%

- 30颗样品零失效(JESD22-A114)

五、工程实践案例

28nm CMOS USB3.1接口ESD防护方案

- 需求:5Gbps速率,HBM 2kV防护

- 方案:

- I/O Pad:低电容二极管串(Cj=0.3pF)

- 电源钳位:RC触发MOSFET(W=500μm)

- 布局:ESD单元与核心电路间距>10μm(防闩锁)

结果:通过HBM 3kV测试,信号眼图抖动<5%

结语

CMOS ESD防护是工艺、器件与系统设计的协同工程。核心设计原则:

- 分级防护:I/O Pad初级保护 + 电源钳位次级保护

- 热管理优化:避免局部热点(扩散区设计/布局规划)

- 工艺适配:FinFET需3D结构,高压接口用级联技术