PCB布局:TVS二极管最短泄放路径设计

PCB布局:TVS二极管最短泄放路径设计

在EMC实验室里,同样的TVS二极管,同样的±30kV ESD枪,为什么别人的板子一次通过,你的板子却屡战屡败?答案可能藏在几毫米的PCB走线里。TVS器件的响应速度可达0.3纳秒,但如果泄放路径长了5mm,寄生电感就会把钳位电压抬高8V,让价值数美元的芯片直接见上帝。布局不是玄学,而是决定防护成败的硬科学。今天咱们就聊聊,怎么给TVS二极管修一条"闪电侠"级别的泄放跑道。

一、核心概念的定义与区分

1.1 泄放路径:ESD电流的"高速公路"

泄放路径指ESD电流从入侵点(连接器引脚)→TVS器件→地平面→电源/机壳地的完整回路。这条路径必须满足三个硬指标:短、粗、直。

短:路径长度每增加1mm,寄生电感增加约0.8nH,在30A/ns的ESD电流下产生24V额外压降。阿赛姆实测显示,TVS距连接器3mm时钳位电压8.5V,距8mm时升至16.2V,防护效能直接腰斩。

粗:TVS接地走线宽度≥2mm,承载瞬时大电流。0.3mm走线在100A冲击下会熔断。某路由器雷击失效案例,接地线宽0.2mm,浪涌电流在走线上产生30V压降,后端PHY芯片直接烧毁。

直:路径禁止拐弯,90°直角使阻抗突变,辐射增加。必须拐弯时采用45°或圆弧,曲率半径≥3倍线宽。

1.2 环路面积:EMI辐射的"放大器"

TVS与被保护器件的环路面积必须<25mm²,否则成为意外天线,辐射强度上升5dBμV/m。某智能手表因环路面积30mm²,FCC认证辐射超标3dB,整改时把TVS从7mm挪到2mm,环路面积缩至8mm²,认证通过。

1.3 寄生电感:钳位电压的"隐形杀手"

过孔电感公式估算:单个0.2mm直径、0.6mm高度的过孔电感约0.5nH。TVS接地用单过孔时,总电感1.5nH(器件引线+过孔),导致钳位电压上升4.5V。改用4个过孔并联,电感降至0.3nV,电压波动仅1V。

阿赛姆实战:ESD5M020TR-5L(SOT23-5L)因封装限制只能打2个过孔,实测钳位电压波动±1.2V;而ESD0303LR(DFN2510)可打8个过孔,波动仅±0.3V,更适合高速信号。

二、匹配的逻辑与准则

2.1 距离优先:越近越安全的铁律

黄金距离:TVS到连接器引脚≤3mm,到被保护芯片≤5mm,到地平面过孔≤1mm。这是IEC 61000-4-2测试无数血泪总结出的经验值。

优先级排序:按响应速度从快到慢,器件排列顺序为ESD二极管→TVS→GDT→压敏电阻。最靠近连接器的必须是ESD二极管,负责第一波钳位。

反例警示:某工业相机TVS距网口15mm,雷击后PHY芯片损坏。整改时将TVS移至3mm,并增加2mm宽接地铺铜,问题解决。

2.2 接地设计:低阻抗是生命线

接地过孔数量:至少4个0.2mm过孔,阵列呈2×2分布,过孔边缘距焊盘0.1mm。4个过孔并联可将阻抗从单孔15mΩ降至3mΩ。

接地铺铜宽度:铜皮宽度>0.2×Ipp(A)。对于50A浪涌,至少10mm宽铜皮或整面铺铜。SM8566J 的散热焊盘需铺铜10mm²以上,否则热阻从15℃/W升至25℃/W,功率循环寿命减半。

星型接地拓扑:所有TVS的接地汇总至一个星型节点,再通过3个以上过孔连接主地平面,避免地环路干扰。

2.3 布线优化:阻抗匹配的精细化

走线宽度:泄放路径走线≥0.3mm,承载瞬时大电流。对于 SMB15J 这类1500W器件,走线宽度需≥0.5mm。

差分信号对称:高速差分对的两线TVS布局必须镜像对称,长度差<0.1mm,间距差<0.02mm。不对称导致共模噪声增加8dB。

禁止跨越分割:TVS下方地平面必须完整,禁止开槽或分割。分割缝隙导致回流路径延长5mm,电感增加4nH。

2.4 禁布区设置:远离敏感信号

TVS周围5mm范围内禁止布置时钟线、复位线、ADC输入等敏感信号,防止ESD泄放时的电磁耦合。某呼吸机在15kV空气放电测试中失效,原因就是TVS紧邻晶振走线,ESD噪声耦合导致时钟抖动超标。

三、关键矛盾与权衡

3.1 空间限制与防护效能的博弈

矛盾:Type-C接口引脚间距0.5mm,TVS封装最小DFN0603(0.6mm×0.3mm)勉强能放,但接地铺铜面积无法保证4mm²,热阻达80℃/W,影响寿命。

权衡:牺牲部分寿命换取空间。阿赛姆 ESD3V3E0017LA 在可穿戴设备中铺铜仅2mm²,热阻60℃/W,但功耗仅0.5W,结温<70℃,寿命仍>1000次循环,满足产品3年寿命要求。

3.2 成本与性能的天平

矛盾:SM8566J性能优异但价格0.18美元,SOD-123封装TVS仅0.03美元但防护能力不足。

权衡:分级防护架构。电源入口用 CVR4532-470V 压敏电阻(0.025美元)吸收80%能量,后端用 SMB15J(0.06美元)精细钳位,总成本0.085美元,比单颗 SM8566J 节省53%,且防护效果相当。

3.3 信号完整性与防护强度的拉扯

矛盾:低电容TVS(如 ESD0524V015T,0.05pF)防护能力强但成本0.082美元,普通TVS( ESDSR05,5pF)成本低但会衰减12Gbps信号。

权衡:HDMI 2.1接口必须用 ESD0524V015T,USB 2.0可用 ESDSR05。某电视厂商为省成本在HDMI口用5pF TVS,眼图裕度从120mV降至30mF,4K@120Hz模式花屏,最终返工更换所有TVS,损失超百万。

3.4 多器件协同与寄生参数叠加

矛盾:多通道TVS阵列(如 ESD0303LR)集成6路防护,但通道间电容耦合导致串扰。

权衡:通道间距保持0.5mm,中间插入接地隔离带,串扰可控制在-45dB以下。若间距缩至0.3mm,串扰恶化至-35dB,眼图抖动增加10ps。

四、选型流程总结

四步打造最短泄放路径:

第一步:接口分析

- 识别所有ESD入侵点(USB、网口、按键、天线)

- 测量每个接口的可用布局空间

- 确定信号速率与芯片耐压

第二步:器件选型

- 速率>10Gbps:选 ESD0524V015T(0.05pF)

- 速率1-10Gbps:选 ESD5M020TR-5L(0.6pF)

- 速率<1Gbps:选 ESD5D150TA(0.05pF,成本低)

- 电源入口:选 SMB15J 或 SM8566J

第三步:布局布线

- TVS距接口≤3mm,画线时从引脚直接出线,禁止拐弯

- 接地焊盘下方打4个0.2mm过孔,过孔距焊盘边缘0.1mm

- 走线宽度≥0.3mm,铺铜面积≥4mm²

- 在丝印层标注禁布区,提醒其他工程师远离

第四步:仿真验证

- 使用SI9000计算走线阻抗,确保差分线100Ω±5%

- 用SIwave仿真环路电感,目标<1nH

- 实测TDR曲线,确认TVS放置后阻抗无突变(偏差<2Ω)

- 打样后进行±30kV ESD枪实测,记录钳位电压波形

阿赛姆实战锦囊:

- 提供免费PCB Layout评审服务,48小时内出具优化报告

- 所有型号提供S参数模型,可直接导入Cadence进行信号完整性仿真

- 深圳EMC实验室配备2.5GHz示波器与ESD枪,可为客户实测验证

记住:PCB布局没有"差不多",只有"达标"与"失效"。TVS到连接器的3mm距离,不是建议,是生死线。走好这3mm,你的产品就能在静电风暴中安然无恙。

关于阿赛姆电子

阿赛姆(ASIM)专注TVS二极管PCB布局优化,提供 ESD5M020TR-5L(SOT23-5L)、ESD0303LR(DFN2510)、SM8566J(SMC)等全系列封装器件,均配备详细布局指导与S参数模型。其深圳EMC实验室配备3GHz示波器、TDR测试仪与ESD枪,可为客户实测泄放路径电感、钳位电压波动与功率循环寿命,确保设计方案一次通过IEC 61000-4-2 ±30kV认证。所有型号提供AEC-Q101车规认证与UL安全认证,是工业、医疗、消费电子领域PCB布局优化的可靠伙伴。

相关新闻

2025.02.26

TVS二极管在汽车电源的保护方法

2025.03.03

通讯线路如何加tvs二极管

2025.03.04

TVS静电防护二极管选型要注意哪些参数?

2025.03.17

TVS管中的开路和短路有什么区别?

2025.03.22

TVS瞬态抑制二极管的钳位电压与工作原理

2025.03.22

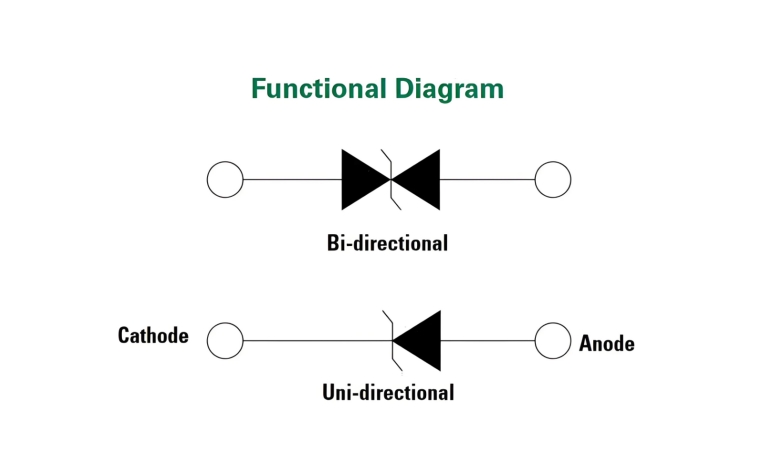

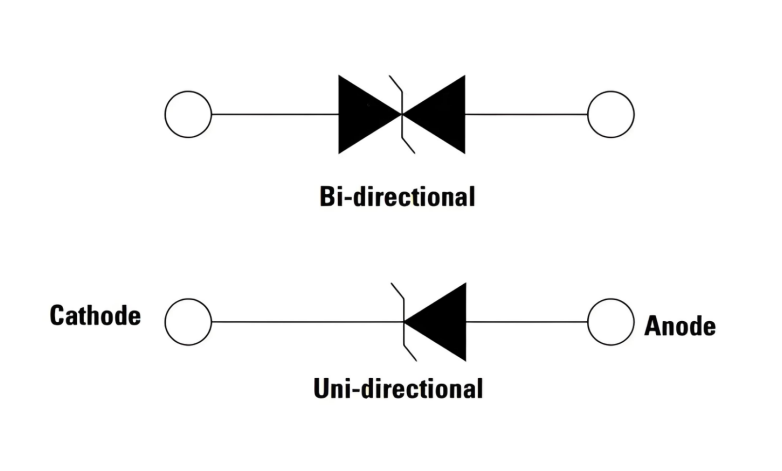

双向TVS二极管和单向TVS二极管有什么区别?

2025.03.27

通信信号浪涌保护TVS二极管怎么选?

2025.04.08

双向TVS管都有哪些优势?如何区分TVS管的极性

2025.04.14

瞬态抑制TVS二极管选型需要注意的七点

2025.04.14

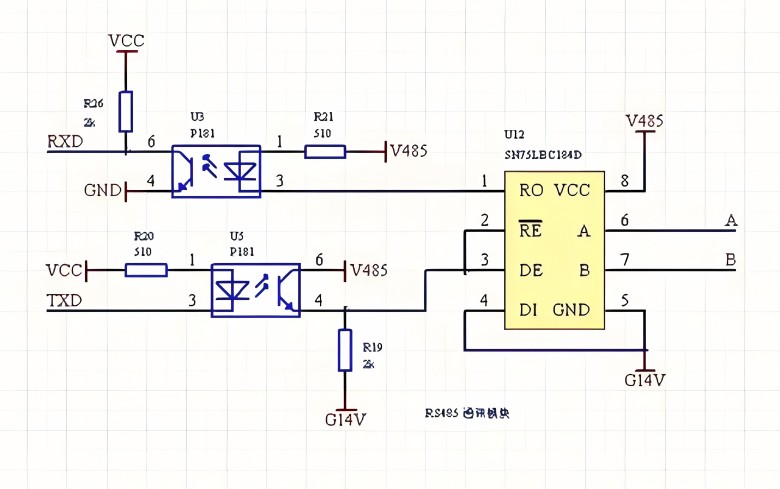

TVS二极管在RS-485通讯线路的应用