ESD管信号端口寄生电容匹配设计方法:确保高频信号完整性的关键实践

在高速数字与射频电路设计中,ESD保护器件的寄生电容已成为信号完整性瓶颈。过大的寄生电容会导致信号边沿退化、阻抗失配和眼图闭合,直接影响产品性能与认证结果。本文基于工程实践,系统阐述寄生电容匹配设计方法,助力工程师实现可靠防护与信号质量的双重目标。

一、明确设计约束条件

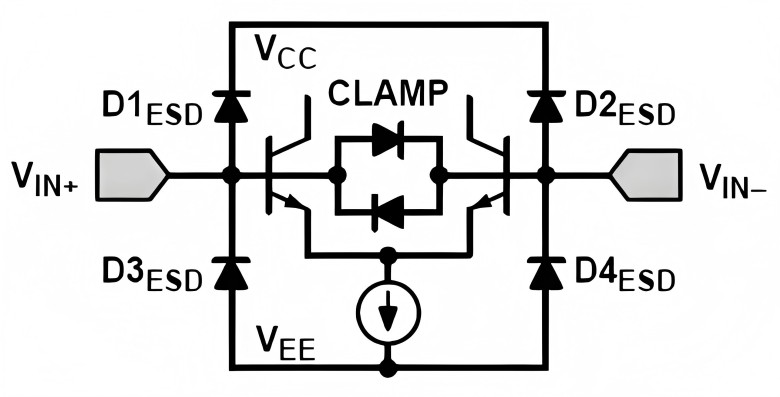

设计始于对端口特性的精确界定。信号速率决定容抗上限,10Gbps差分信号要求单端寄生电容低于0.5pF,25Gbps需低于0.2pF。阿赛姆的ESD3625QSA系列专为10Gbps设计,寄生电容仅0.25pF,而ESD0524PA系列满足25Gbps,电容低至0.1pF。

接口标准同样是硬约束。USB 3.2 Gen2要求寄生电容小于1pF,HDMI 2.1需低于0.8pF。汽车以太网100BASE-T1标准更严苛,单端口电容必须小于0.15pF。选型时必须核对规范,避免设计返工。

ESD防护等级不可妥协。IEC 61000-4-2 Level 4要求接触放电8kV、空气放电15kV。阿赛姆ESD0524PA在0.1pF电容下仍能实现±8kV接触放电,打破"低电容低防护"的传统认知,其秘诀在于优化的器件结构与工艺。

工作电压范围影响电容稳定性。5V系统可选ESD3605SA系列,30V系统需ESD3630SA系列。值得注意的是,TVS二极管在反向偏置时电容随电压升高而下降,选型时应参考阿赛姆数据手册中C-V特性曲线,确保全电压范围内电容波动小于20%。

二、寄生电容的来源与特性

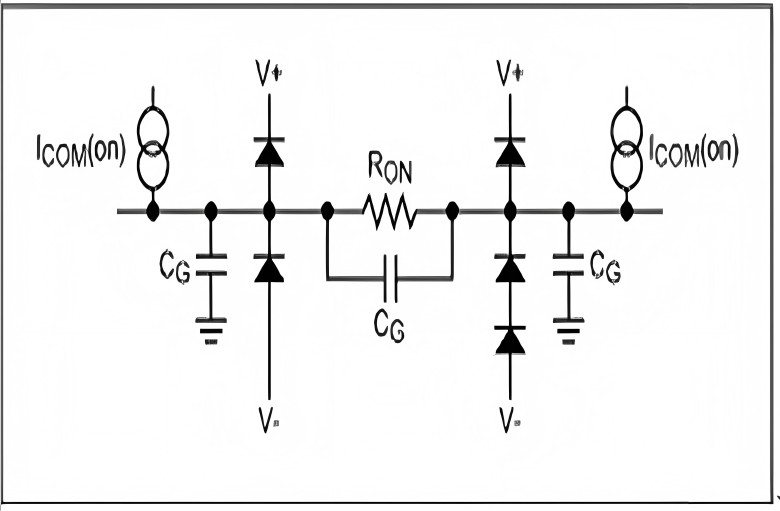

ESD保护器件的寄生电容主要来源于PN结耗尽层电容。二极管型ESD在反向偏置时,空间电荷区宽度随电压增加而扩大,导致电容减小。阿赛姆ESD3625QSA在0V偏压下电容0.3pF,5V偏压时降至0.25pF,这种非线性特性必须在匹配设计中予以考虑。

封装引入额外寄生参数。SOT-23封装引线电感约2nH,DFN0603封装可降至0.5nH。更关键的是封装与芯片间键合线电容,约0.05-0.1pF。阿赛姆DFN封装系列产品通过晶圆级封装技术消除键合线,将总电容降低30%以上。

PCB走线同样贡献寄生电容。50Ω微带线每毫米约0.05pF,BGA焊盘约0.02pF。在高频设计中,1mm走线差异可导致阻抗失配2Ω。因此,ESD器件布局应尽量靠近被保护端口,缩短走线长度。

温度特性不可忽视。结温从25℃升至85℃,寄生电容增加约5%。汽车级产品如阿赛姆ESD3605QSA通过特殊掺杂工艺,将温漂控制在3%以内,确保全温度范围匹配精度。

三、寄生电容匹配的核心设计方法

阻抗再匹配(Re-Matching)技术:这是最成熟的方法。先完成无ESD时的端口阻抗匹配,再将ESD器件等效电容加入仿真,通过调整匹配网络电感或电容值重新建立阻抗匹配。5GHz LNA案例显示,未匹配时ESD导致增益下降4-14%,NF恶化11-18%;再匹配后增益损失恢复76-82%。阿赛姆提供SPICE模型,支持在ADS等工具中精确仿真。

T-coil补偿技术:在ESD器件前后各串联一个电感,形成T型网络。该结构利用谐振原理抵消电容的低通效应,可将带宽提升2.7倍。对于1pF的ESD电容,串联3nH电感可在10GHz频率内实现全频段匹配。阿赛姆ESD3625QSA与T-coil组合已成功应用于25Gbps SerDes端口设计。

二极管尺寸优化:增大二极管叉指数量可提升ESD防护能力,但会线性增加寄生电容。设计需在防护等级与电容间折中。阿赛姆采用多叉指并联结构,通过优化叉指间距与布局,在同等电容下将耐流能力提升40%。ESD0524PA采用8叉指设计,在0.1pF电容下实现8kV防护。

协同设计流程:将ESD器件作为匹配网络的一部分进行联合优化。步骤包括:1)获取器件S参数;2)去嵌测试夹具影响;3)插入电路仿真;4)整体优化匹配元件。阿赛姆提供GSG共面测试结构数据,支持客户进行精确去嵌。

差分对匹配:高速差分线需保证两线电容对称。采用ESD0524PA等集成双通道器件,两通道电容偏差小于0.01pF,确保差分对间时序偏差小于1ps,眼图抖动降低30%。

四、设计验证与测试

S参数测试:使用矢量网络分析仪测量端口回波损耗。目标是在工作频段内S11优于-15dB。测试前需进行开路、短路、负载校准,并采用去嵌技术消除测试夹具影响。阿赛姆提供标准去嵌方法文档,指导客户获得器件本征S参数。

眼图测试:在10Gbps速率下,插入ESD保护后眼图张开度应保持在85%以上。使用BERT配合示波器测量,模板裕量需大于15%。ESD3625QSA在12.5Gbps USB3.2信号测试中,眼高保持800mV以上,满足规范要求。

ESD应力测试:按IEC 61000-4-2标准施加8kV接触放电,残余电压需低于被保护芯片耐压的80%。测试时需监测信号完整性,确保ESD冲击后眼图无退化。阿赛姆全系列ESD产品均通过8kV/15kV认证,提供第三方测试报告。

温度循环验证:在-40℃至85℃范围内进行100次温度循环,测量电容变化率应小于5%。汽车级产品ESD3605QSA实测变化率仅2.1%,满足AEC-Q100 Grade 0要求。

五、设计注意事项

避免电容叠加陷阱:多颗ESD器件并联时,电容线性叠加。保护8个端口时,若每颗电容0.3pF,总电容达2.4pF,将严重破坏信号完整性。应选用集成多通道器件,如ESD0524PA单颗保护4通道,总电容仅0.1pF。

布线对称性:差分对保护器件布局必须对称,走线长度差异小于0.5mm。不对称引入的时延差会导致共模噪声转差模,增加误码率。阿赛姆DFN封装器件提供对称引脚布局,便于PCB对称布线。

电源去耦:ESD泄放时会在电源平面产生噪声干扰。应在ESD器件附近并联0.1μF与10nF陶瓷电容,将电源噪声抑制在50mV以内。阿赛姆建议电源平面与信号平面间距保持0.2mm以上,避免噪声耦合。

ESD路径最短原则:电荷泄放路径长度决定残余电压。从ESD器件到地的走线长度应小于5mm,过孔数量不超过2个。使用阿赛姆产品时,推荐将器件地脚直接连接至系统地平面,避免经过细长线。

批次一致性:不同批次器件电容存在±10%偏差。量产时需对首批100片进行S参数抽检,确保电容一致性。阿赛姆DFN封装产品通过晶圆级测试,批次一致性控制在±5%以内,减少量产匹配调试工作量。

模型准确性:供应商提供SPICE模型需包含寄生参数。阿赛姆官网提供ESD3625QSA等全系列产品的完整模型库,包含温度特性与C-V曲线,可直接导入ADS、Cadence等仿真平台,避免"仿真OK实测失败"的陷阱。