Type-C接口ESD管正反插防护真能无死角?

Type-C 接口的 ESD(静电放电)防护无法做到绝对无死角,但合格的 ESD 防护方案可以实现接近无死角的双向防护,满足绝大多数应用场景的静电防护需求。

一、Type-C 接口的物理特性决定双向防护基础

24 针脚的对称布局

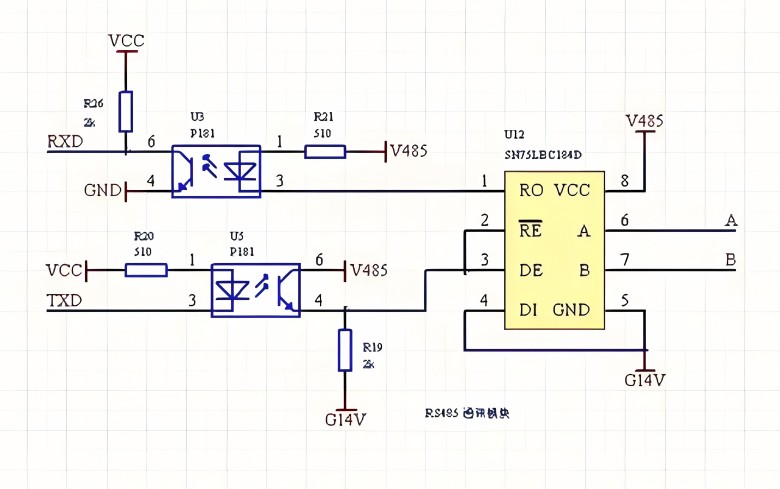

Type-C连接器采用中心对称设计,A 面与 B 面各 12 针,CC1/CC2 用于方向识别,VBUS、GND、TX±、RX±、SBU1/2 等信号在两面镜像分布。无论正插或反插,VBUS 始终对应 VBUS,TX1± 与 TX2± 通过复用器切换,RX 同理。这种物理对称性为"双向防护"提供了硬件基础——同一组信号线不会因地线错位而悬空。电源路径的独立性

VBUS 与 GND 在两面各有两组触点,实际焊接时合并为同一网络;CC 线仅有一面接通(CC1 或 CC2),但 ESD 保护器件通常并联在 CC1 与 CC2 之间,确保无论哪条 CC 线被激活,防护网络均在线。高速差分线的极性容错

USB3.x/4 的 TX/RX 差分对支持极性翻转(Polarity Flip),即使插头旋转 180°,差分信号的 P/N 极性由 PHY 层自动纠正,ESD 管只需保证差模钳位对称即可,无需区分正反。

二、ESD 管的选型和方案设计是关键

信号完整性优先

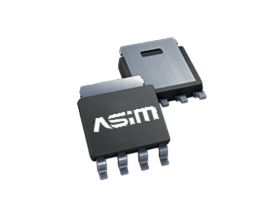

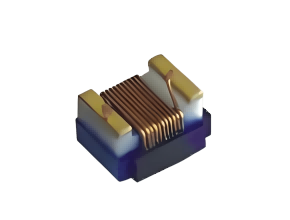

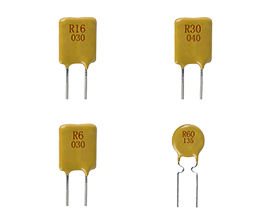

USB3.2 Gen2 10 Gbps 要求 ESD 管结电容 < 0.3 pF,USB4 40 Gbps 需 < 0.15 pF。阿赛姆 ASIM ESDULCxx 系列采用深回刻工艺,0.15 pF 容值下仍可保证 ±30 kV 空气放电,眼图裕量 > 30 %。全信号覆盖的器件矩阵

VBUS (5 V/20 V):ASIM SMBJ20CA,600 W 峰值功率,钳位电压 < 30 V

CC1/CC2 (5 V 逻辑):ASIM ESD5V0D3-ULC,0.25 pF,±20 kV 接触

SBU1/2 (Sideband Use):ASIM ESD5V0D5,双向对称钳位

TX/RX 差分对:ASIM ESDULC5V0D3-B,0.15 pF,回波损耗 <-20 dB @ 10 GHz

D+/D- (USB2.0):ASIM ESD5V0D4,4 通道阵列,节省 60 % 布板空间

布局的"就近原则"

ESD 管焊盘距 Type-C 连接器金属壳 < 3 mm,差分线先经过 ESD 管再进入 AC 耦合电容,禁止在 ESD 管与连接器之间走 stubs。地回路通过 4-6 个 0.3 mm 过孔直下主地平面,降低寄生电感。

三、“死角” 的潜在来源

机械结构的物理盲区

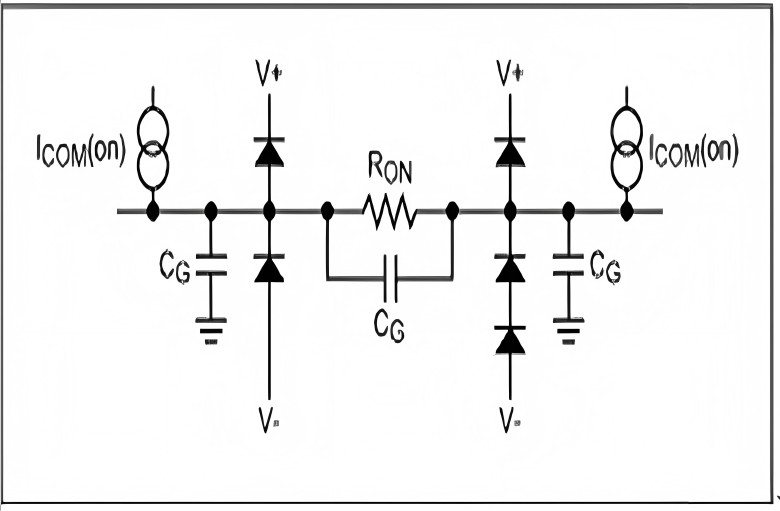

Type-C 插头插入时,金属外壳与插座外壳先接触,信号针脚后接触;拔出时顺序相反。若外壳接地不良(如浮动设计),静电可能通过外壳耦合至未完全接通的信号针脚,形成"插入瞬态"放电。实测中,此过程持续 50-200 μs,普通 TVS 响应足够,但若外壳与板地之间仅通过 1 MΩ 电阻连接,电荷积累可达数百伏,击穿未上电的芯片 GPIO。协议切换的电压窗口

PD 快充协商阶段,VBUS 从 5 V 跃升至 20 V,若 ESD 管 V_RWM 仅按 5 V 设计(如 5.5 V),升压瞬间 TVS 进入击穿区,产生 mA 级漏电流,长期热积累导致器件劣化。阿赛姆 ASIM 方案在 VBUS 路径采用 24 V 器件(V_RWM=24 V),覆盖 20 V 充电+20 % 裕量,避免协议切换盲区。高速信号的差模-共模转换

差分对 ESD 管若布局不对称(如 P 线 ESD 管距连接器 2 mm,N 线 5 mm),正反插时因路径长度差异产生 20-50 ps 时滞,高速信号(>10 Gbps)眼图闭合,误码率上升。此"时序死角"与 ESD 防护能力无关,但会导致系统级失效。未使用引脚的悬空风险

Type-C 母座中 SBU1/2 在 USB3.x 模式下闲置,若未接 ESD 管且软件配置为高阻输入,静电注入后可诱导闩锁(Latch-up)。阿赛姆 ASIM 建议在 SBU 线统一放置 0.5 pF 级 ESD 管,成本增加 < 0.05 USD,消除悬空隐患。测试方法的局限性

IEC 61000-4-2 接触放电仅针对金属外壳可触及点,Type-C 内部针脚在插入状态下被塑料舌片遮挡,标准测试无法覆盖。实际工况中,用户手指可能触碰插头金属壳(已接地)与设备金属壳(未接地)之间,形成间接放电路径,此场景需额外进行"系统级 ESD"测试(IEC 61000-4-2 附录 E)。

四、设计验证的补充要点

全方向插拔测试

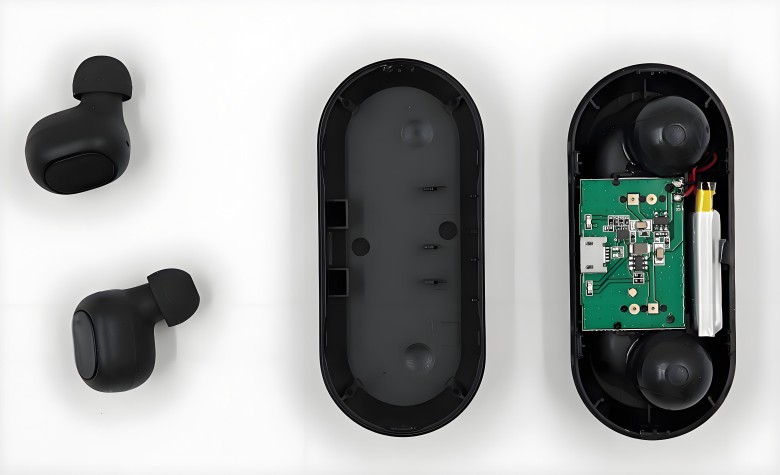

正插、反插各 100 次,同时进行 ±8 kV 接触放电,检查 CC 线逻辑是否误触发、VBUS 是否掉电。阿赛姆 ASIM 提供测试夹具与报告模板,覆盖 0°/180° 双方向。温度循环后的 ESD 复测

-40 ℃↔85 ℃ 循环 500 次后,塑封体与 PCB 热膨胀系数差异可能导致焊点微裂,ESD 路径阻抗上升,钳位电压漂移 > 10 % 即判定失效。共模电流路径分析

用近场探头扫描 Type-C 区域,识别 ESD 放电时共模电流是否流经敏感芯片底部,必要时在连接器与芯片之间增加屏蔽地过孔墙。

结语

Type-C 的对称物理结构为双向防护提供了先天条件,但"无死角"需要器件选型、布局细节、协议裕量、测试方法四重叠加。金属壳接地不良、协议电压跃迁、高速时序偏差、未用引脚悬空——任何一环的疏忽都会制造真实盲区。阿赛姆 ASIM 的 Type-C 方案从 5 V 慢充到 240 W PD3.1、从 USB2.0 到 USB4 40 Gbps 均有对应料号,数据手册标注全温区钳位电压曲线,拒绝用常温数据冒充全场景防护。下次评审 Type-C 防护方案,建议把"死角"清单逐条核对,用实测报告代替口头承诺。