技术咨询

微信咨询

您需要进一步的协助吗?

请告诉我们您的具体研究需求,我们将尽快回复您。

![]()

验证码*

行业方案

专业,用心为每一位客户提供最前沿的方案支持

按行业分类

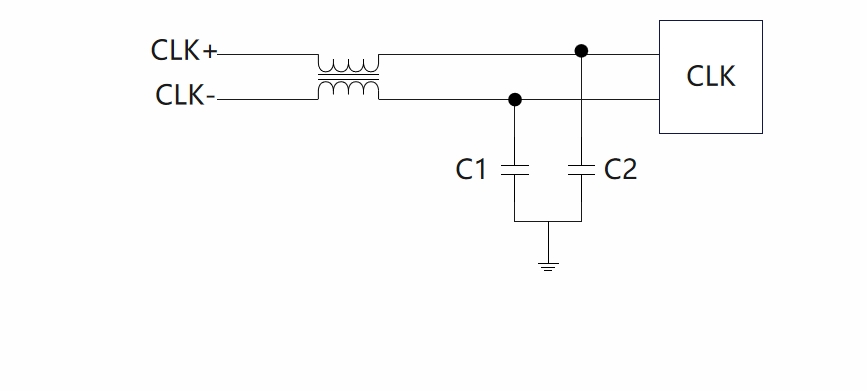

差分时钟电路设计方案

差分时钟 EMC 电路设计方案