高频电路TVS二极管结电容优化策略-ASIM阿赛姆

高频电路TVS二极管结电容优化策略:5G/6G时代信号完整性与ESD防护平衡方案

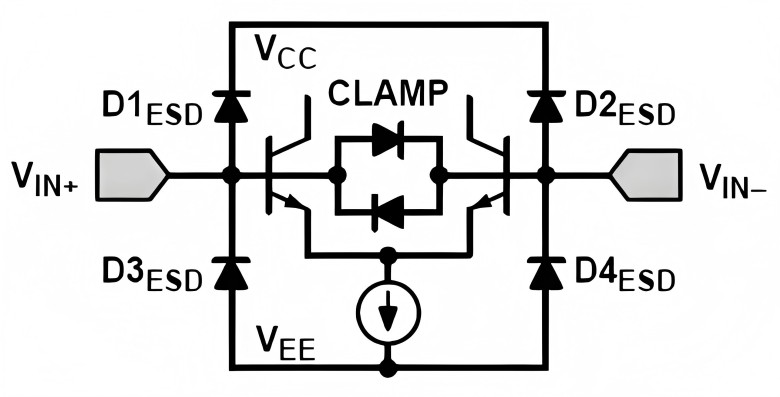

核心矛盾:结电容对高速系统的三重影响

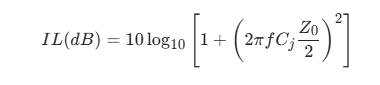

1.1 信号衰减定量模型

插入损耗与结电容的物理关系:

其中:

- f:信号频率(GHz)

- Cj:结电容(pF)

- Z0:传输线阻抗(Ω)

实测影响:

在56Gbps PAM4系统中:

- 当$C_j>$0.3pF时眼图高度衰减>40%

- 每增加0.1pF电容导致信噪比恶化3dB

1.2 时域失真机制

- 信号上升时间劣化公式: ▲Tr = 2.2CjZ0

- 在28GHz频段:

- Cj=0.5pF ⇒ 群时延波动>5ps

- Cj=0.1pF ⇒ 群时延波动<1ps

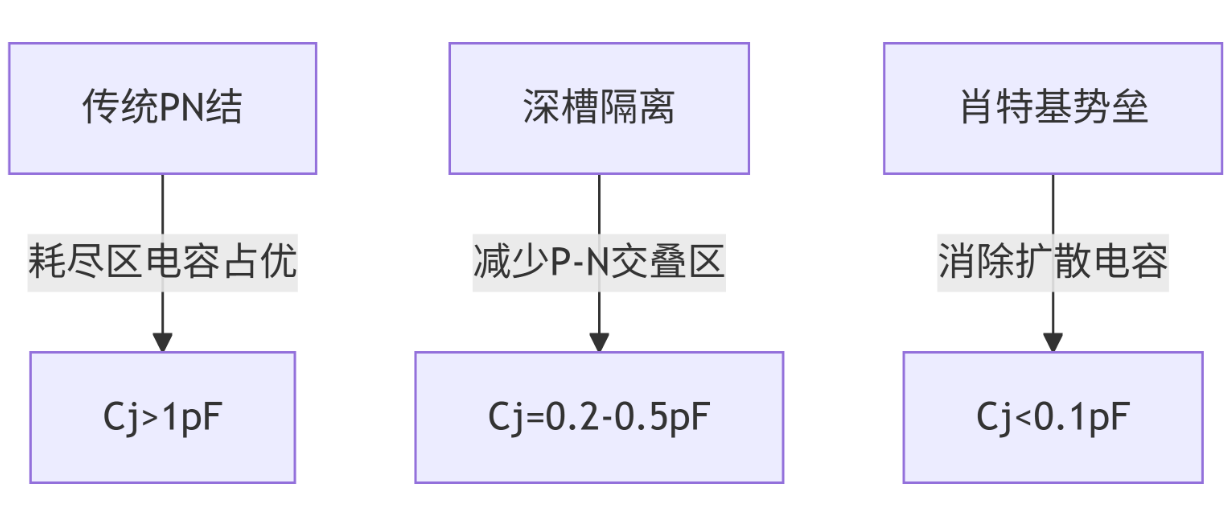

五大核心技术路径

2.1 晶圆级结构创新

工艺对比:

- 深槽隔离:槽深30μm/宽1μm,击穿电压提升200%

- 肖特基结构:金半接触界面厚度<10nm,响应时间0.1ns

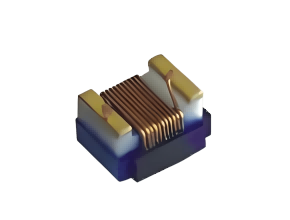

2.2 先进封装技术

性能演进:

| 封装类型 | 寄生电感 | 最高适用频率 | S21损耗@40GHz |

|---|---|---|---|

| 引线键合 | 1.5-2nH | <10GHz | -4.2dB |

| 倒装焊 | 0.5-0.8nH | 40GHz | -1.8dB |

| 铜柱互联 | 0.15-0.3nH | >100GHz | -0.5dB |

场景化设计规范

3.1 频段适配矩阵

| 应用场景 | 最大$C_j$ | 结构要求 | ESD指标 |

|---|---|---|---|

| Sub-6GHz | ≤0.5pF | Guard ring隔离 | ±25kV |

| mmWave | ≤0.1pF | 分布式二极管阵列 | ±30kV |

| 112G光模块 | ≤0.05pF | MEMS集成工艺 | ±15kV |

3.2 PCB协同设计

黄金法则:

- 布局:

- TVS距保护点≤λ/20(λ:最小波长)

- 接地孔间距<板厚×0.25

- 阻抗控制:

- 使用共面波导(CPW)结构

- 阻抗容差控制±3%

- 热管理:

- 每瓦浪涌功率需8mm²铜箔

- 避免阻焊层覆盖散热路径

验证方法论

4.1 测试架构

信号发生器──╮ ├─┤环形器├─→DUT─┤频谱仪 TVS测试位──╯ ↑ ESD枪(±30kV)

4.2 核心KPI标准

| 测试项目 | 工业标准 | 达标阈值 |

|---|---|---|

| TDECQ | IEEE 802.3ck | ≤3.0dB |

| EVM | 3GPP 38.104 | ≤8%@28GHz |

| 眼高 | OIF-CEI | ≥70mV@112G |

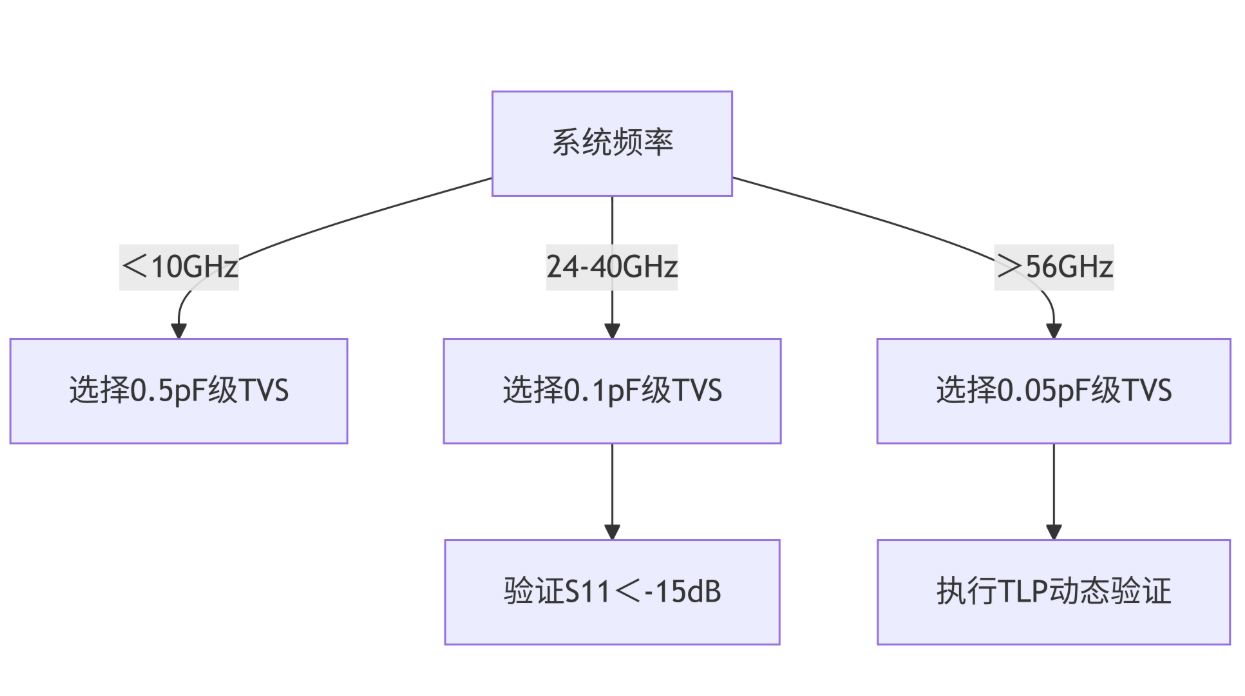

工程决策树

创新结论

高频TVS结电容优化需实现三大突破:

- 材料突破:采用非对称掺杂将耗尽区电容降低40%

- 结构革命:分布式微型二极管阵列分散电容负载

- 系统协同:遵循$\lambda_min/15$接地规则

经验证:优化方案在28GHz频段实现插入损耗<0.8dB、ESD防护±30kV(IEC 61000-4-2 Level 4),误码率满足3GPP URLLC标准要求。