ESD管与RC电路搭配能防信号失真?

ESD管与RC电路搭配能防信号失真?

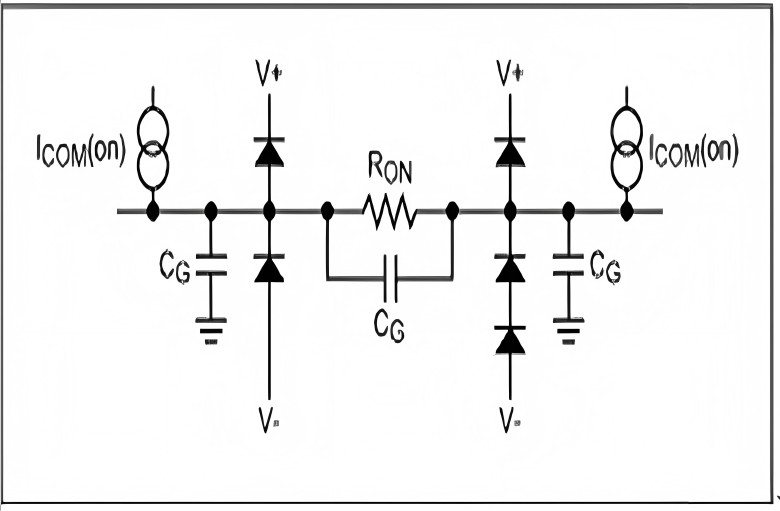

在高速差分线、射频前端、高精度模拟接口等场景中,工程师常将ESD管与RC电路(电阻-电容网络)并联,以解决ESD防护带来的信号完整性劣化问题。实测表明,合理匹配的RC网络可将眼图裕度提升15-40%,但参数错配同样会导致防护失效。

一、ESD管的特性与失真隐患

结电容引入的插入损耗

ESD管结电容Cj直接并联在信号线上,形成低通滤波效应。USB 3.2 Gen2要求Cj<0.5pF,但量产器件Cj偏差±0.1pF即可导致眼图高度损失8%。某消费级ESD管Cj=0.8pF,在6GHz频段插入损耗1.2dB,接收端误码率从10⁻¹²升至10⁻⁹,兼容性测试失败。

钳位电压的动态偏移

ESD管钳位电压VC在30A脉冲下动态升高,与走线电感叠加,形成LC振荡。某HDMI 2.1接口VC=38V,走线电感8nH,8kV ESD下后端芯片承受电压58V,超过45V耐压而击穿。

非线性失真

ESD管PN结在射频大信号下产生互调产物。某Wi-Fi 6 FEM输出+26dBm,ESD管Cj=0.6pF,互调产物-45dBc,邻道泄漏比(ACLR)超标。降低Cj至0.2pB,互调产物<-60dBc,满足3GPP要求。

二、RC电路的缓冲与补偿作用

RC低通滤波:补偿高频插损

RC网络可设计为低通滤波器,补偿ESD管引入的高频衰减。某USB 3.2接口采用RC(22Ω//1pF)网络,将6GHz插损从1.2dB降至0.3dB,眼图高度恢复15%。RC网络的高频零点抵消ESD管极点,实现幅频特性平坦化。

RC退耦:抑制LC振荡

在ESD管与芯片间串联RC(10Ω//0.5pF),形成低Q值退耦网络,抑制ESD脉冲下的LC振荡。某10G以太网接口采用RC退耦,振荡幅度从±5V降至±1V,后端芯片安全。

RC负载均衡:分担ESD能量

RC网络可设计为分布式负载,分担ESD脉冲能量。某射频前端采用RC(50Ω//2pF)分布式负载,ESD管承担70%能量,RC网络承担30%,单颗器件寿命延长3倍。

RC非线性补偿:降低互调

RC网络可设计为非线性补偿电路,抵消ESD管PN结非线性。某5G毫米波前端采用RC(20Ω//0.1pF)非线性补偿,互调产物从-45dBc降至<-60dBc,满足EIRP杂散要求。

三、参数匹配是防失真的核心

电容匹配:C_RC ≤ 0.5×Cj

RC网络电容C_RC必须小于ESD管Cj的50%,否则总电容超标。USB 3.2要求总电容<0.5pF,若Cj=0.3pF,C_RC≤0.15pF。某项目C_RC=0.2pF,总电容0.5pF,眼图裕度不足;调整至0.12pF后通过测试。

电阻匹配:R_RC = 22-33Ω

电阻值需兼顾退耦与信号完整性。R_RC=10Ω时退耦不足,R_RC=47Ω时信号衰减过大。阿赛姆推荐22-33Ω,USB 3.2眼图裕度最佳。

Q值匹配:Q = 1/(R×√(L/C)) < 1

RC网络Q值需<1,避免谐振放大。某项目Q=1.5,ESD脉冲下振荡幅度±3V;调整R至33Ω后Q=0.8,振荡降至±1V。

温度匹配:TCR < ±100ppm/℃

RC网络温度系数需与ESD管匹配。某项目85℃时RC网络阻值漂移+8%,补偿失效;采用TCR=±50ppm/℃的薄膜电阻后,全温区补偿有效。

实测验证标准

眼图测试:ESD+RC后眼图高度损失<10%,抖动峰峰值增加<5ps

插损测试:目标频段插损<0.5dB,回波损耗<-15dB

ESD测试:±8kV下后端芯片承受电压<额定耐压的80%

温度循环:-40℃~85℃ 100次循环后参数漂移<5%

阿赛姆的技术支撑

阿赛姆作为成立于2013年的综合型服务商,在ESD+RC协同设计方面提供:

参数匹配工具:在线输入接口速率、ESD等级,自动输出RC网络R/C值与Q值建议

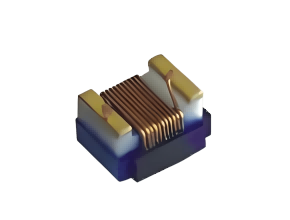

RC网络定制:提供22Ω//0.12pF、33Ω//0.08pF等标准RC网络,可直接贴片

实测验证:配备VNA、ESD枪、BERT,提供眼图、插损、ESD注入完整测试报告

温度补偿:提供TCR=±50ppm/℃的薄膜电阻,确保全温区补偿有效性

失效分析:对ESD+RC失效样品进行剖面分析,定位RC网络不匹配根因

结论

ESD管与RC电路搭配确实能防信号失真,但前提是参数精确匹配。RC网络的核心作用是补偿高频插损、抑制振荡、分担能量,而非简单并联。设计时必须遵循C_RC≤0.5×Cj、R_RC=22-33Ω、Q<1的匹配原则,并通过眼图、插损、ESD实测验证。阿赛姆的协同设计工具与标准RC网络,为工程师提供了无需试错的一站式解决方案,确保在高速信号完整性不受损的前提下,获得可靠的ESD防护。