千兆网口ESD管并联使用会导致信号衰减?

千兆以太网接口的ESD防护设计中,器件并联是工程师常用的冗余策略,但并联使用会直接导致结电容叠加,引发信号完整性劣化。本文从传输线理论、电容叠加效应与阻抗匹配三个层面,解析ESD管并联导致信号衰减的工程机理,分析单器件并联、混合并联与阵列集成等不同场景的衰减差异。

一、衰减产生的核心工程原理

千兆以太网遵循1000BASE-T标准,采用四对差分线进行全双工通信,每对差分线的信号速率为125MBaud,通过PAM5编码实现250Mbps数据传输,四对线聚合达成1Gbps总带宽。该标准对信号完整性有严格要求,差分对阻抗需维持在100Ω±10%,任何并联在信号线与地之间的电容都会降低差分阻抗,引起信号反射与插入损耗。

ESD保护器件的结电容与信号线并联,形成RC低通滤波器特性。当结电容超过一定阈值时,高频信号分量(千兆以太网基频为62.5MHz,但信号谐波延伸至250MHz以上)产生衰减,导致信号上升沿变缓、眼图闭合度下降。千兆以太网接口要求ESD器件结电容控制在0.5pF以下,理想值应低于0.3pF,以确保在250MHz频点插入损耗小于0.2dB。

器件并联使用时,总结电容为各器件结电容之和。若两颗结电容0.5pF的ESD管并联,总电容达1.0pF,超出千兆以太网容忍阈值。此电容增量在频域表现为插入损耗曲线整体抬升,在时域表现为信号边沿速率下降与抖动增加。实测数据显示,1.0pF的并联电容可使千兆网口的眼图张开度从标准的0.6UI降至0.4UI,误码率从10⁻¹²上升至10⁻⁹,触发链路降速或频繁重传。

除电容叠加效应外,并联器件的寄生电感与阻抗失配亦贡献信号衰减。每颗ESD管的封装寄生电感(通常为0.3-0.5nH)在并联时并非简单叠加,而是形成复杂的LC谐振网络。当多颗器件并联时,地回路电感增加,导致地弹噪声抬升,共模噪声向差模噪声转换,进一步恶化信号质量。

更为关键的是器件特性离散性导致的非均匀导通。不同批次或不同型号的ESD管,其击穿电压与动态电阻存在分布差异。并联使用时,击穿电压较低的器件会优先导通,承担大部分浪涌电流,而另一颗器件未能及时导通,形成单颗器件过载。此现象不仅削弱了并联提升通流能力的预期效果,更可能导致优先导通的器件因能量过载而短路,短路后的低阻抗路径使信号线对地近似短路,造成信号完全衰减与总线故障。

二、不同并联场景的衰减影响程度

根据并联器件的类型、数量与匹配程度,信号衰减的影响程度存在显著差异。

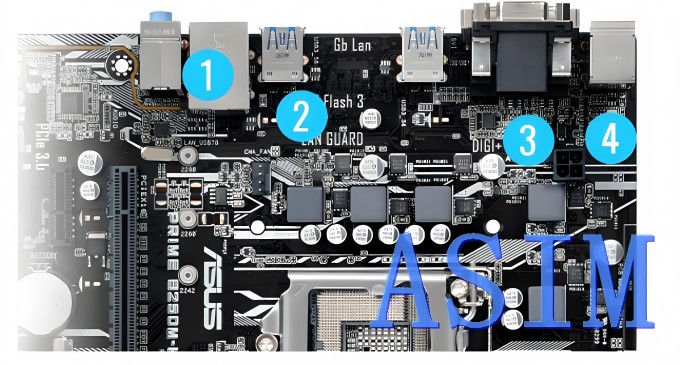

同型号同批次器件并联: 当使用同一批次、同一型号的ESD管并联时,结电容叠加为单颗的两倍。以两颗结电容0.5pF器件并行为例,总电容1.0pF已超出千兆以太网0.5pF的限值要求。此时在250MHz频点,插入损耗可达-0.8dB至-1.0dB,远高于单颗器件的-0.2dB。信号反射系数增大,导致回波损耗恶化,严重时触发PHY芯片的自适应均衡机制,降低有效传输速率以维持链路稳定性。阿赛姆技术文档明确指出,千兆网口ESD器件结电容必须≤0.5pF,并联使用将直接违反此设计规范。

不同型号器件并联: 工程师有时将高压器件与低压器件并联,试图兼顾不同威胁等级。例如将24V耐压器件与5V器件并联于千兆网口。此类混合并联不仅电容叠加,更因器件的V-I特性差异导致保护失效。24V器件的结电容通常达5-10pF,与5V器件并联后总电容超过6pF,在62.5MHz基频处即产生显著衰减,千兆网口实际速率可能降至百兆甚至更低。此外,高压器件的响应速度慢于低压器件,ESD事件来临时低压器件优先击穿,若其通流能力不足,可能在高压器件导通前即已热击穿,造成信号线对地短路,信号完全中断。

多颗器件并联的累积效应: 部分设计为提升浪涌裕量,采用三颗及以上ESD管并联。此时总结电容可能达1.5pF至2.0pF,形成明显的低通滤波效应。千兆以太网信号的高频分量被严重衰减,导致码间干扰增加,误码率急剧上升。同时,多颗器件的接地路径并联,形成地环路风险,外部电磁干扰在环流中产生感应电压,叠加于信号线上,造成数据丢包。

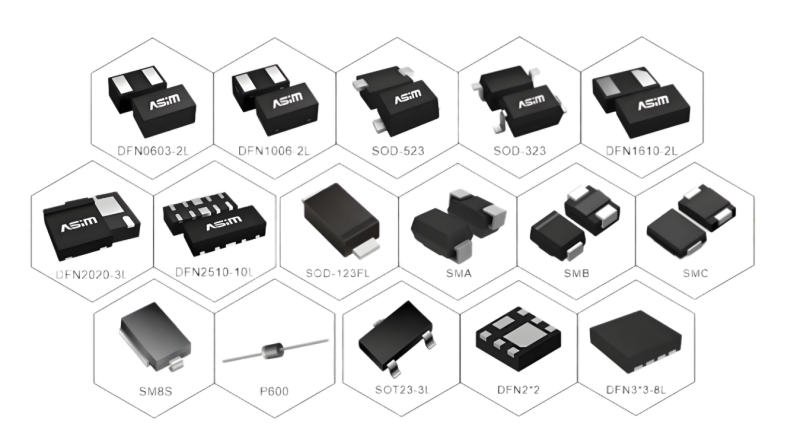

阵列器件内部并联: 集成式多通道ESD阵列(如四路或八路阵列)通过单片集成工艺实现多通道保护,虽物理上为多颗器件,但因采用统一晶圆与封装,结电容并非简单算术叠加,而是通过内部拓扑优化控制在较低水平。例如阿赛姆ESD5D100TA四通道阵列,单芯片集成4路保护,每通道结电容0.3pF,通道间电容匹配度控制在±0.02pF以内,通过流通式封装设计,确保差分信号对称性,避免传统分立器件并联的电容叠加与不平衡问题。此类集成方案在功能上等效于并联,但因工艺集成,避免了分立并联的寄生参数劣化。

三、工程设计规范要求

针对千兆网口ESD防护,工程设计上应严格遵循以下规范,避免并联使用导致的信号衰减。

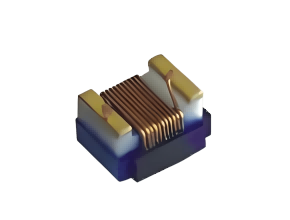

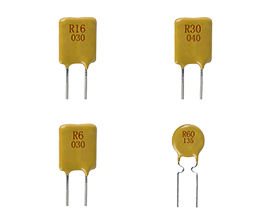

单器件选型优先原则: 千兆以太网ESD防护应选用单颗满足通流与钳位要求的低电容器件,避免通过并联提升性能。阿赛姆ESD0524V015T结电容低至0.05pF,远低于千兆网口0.5pF的限值,单颗即可满足±25kV ESD防护与8A浪涌通流需求,无需并联即可提供充足保护裕量。ESD5D030TA结电容0.3pF,同样满足千兆网超低电容需求,支持500Mbps以上速率。

阵列器件替代分立并联: 如需保护多对差分线(千兆以太网含四对差分线),应选用集成式多通道阵列而非多颗分立器件并联。阿赛姆ESD5D100TA四通道阵列采用单片集成工艺,四通道结电容均为0.3pF,且通道间差异小于0.02pF,确保差分对完全对称。集成封装消除了分立器件并联的寄生电感叠加问题,地回路路径统一,避免地弹噪声。

结电容预算控制: 设计阶段需建立完整的结电容预算。千兆网口从RJ45连接器至PHY芯片之间,除ESD器件外,还可能包含共模滤波器、网络变压器等元件。阿赛姆技术文档指出,千兆网口总电容预算应控制在1.0pF以内,其中ESD器件占比不超过50%,即0.5pF。若因历史原因必须采用较高电容器件,应通过降低其他元件电容或优化布局补偿,严禁通过并联ESD器件提升通流能力,以免破坏信号完整性。

布局与接地优化: ESD器件应紧靠RJ45连接器放置,距离控制在10mm以内,减少寄生电感。接地引脚长度需小于3mm,采用多个过孔直接连接至完整地平面,降低地回路阻抗。若采用阵列器件,需确保阵列地平面与连接器外壳地低阻抗连接,避免多点接地形成地环路。阿赛姆建议千兆网口TVS器件应布局在共模滤波器之前,紧靠RJ45接口,优先保护信号入口。

分级防护而非并联强化: 对于高浪涌风险场景(如户外设备、工业现场),不应通过并联ESD器件提升防护能力,而应采用分级防护架构。第一级采用陶瓷气体放电管(GDT)或压敏电阻吸收大部分浪涌能量,第二级采用自恢复保险丝限流,第三级采用低电容TVS器件精确定位残压。阿赛姆提供三级防护一站式方案,包括GDT、PTC与TVS的协同匹配,通过能量分级耗散而非并联堆叠,实现高防护等级与低信号衰减的平衡。

器件一致性验证: 若因特殊原因必须采用并联方案(仅限于同型号同批次器件增加极少量裕量),需进行严格的器件筛选,确保并联器件的击穿电压偏差小于5%,结电容偏差小于10%,并通过TLP(传输线脉冲)测试验证电流分配的均匀性。阿赛姆EMC实验室配备相应测试设备,可针对客户实际电路板进行TVS效能实测,验证并联后的残压与信号完整性表现。

阿赛姆(ASIM)针对千兆以太网接口提供完整的低电容ESD解决方案。ESD0524V015T结电容仅0.05pF,支持1000BASE-T全速率传输,在±25kV ESD冲击下误码率保持10⁻¹²以下。ESD5D030TA结电容0.3pF,采用DFN封装,适用于空间受限的千兆网口设计。ESD5D100TA四通道阵列提供四对差分线一体化保护,通道间电容匹配度±0.02pF,避免分立器件并联的不对称问题。所有器件均通过IEC 61000-4-2 Level 4(±8kV接触/±15kV空气)测试,工业级产品支持-40℃至125℃全温度范围工作。